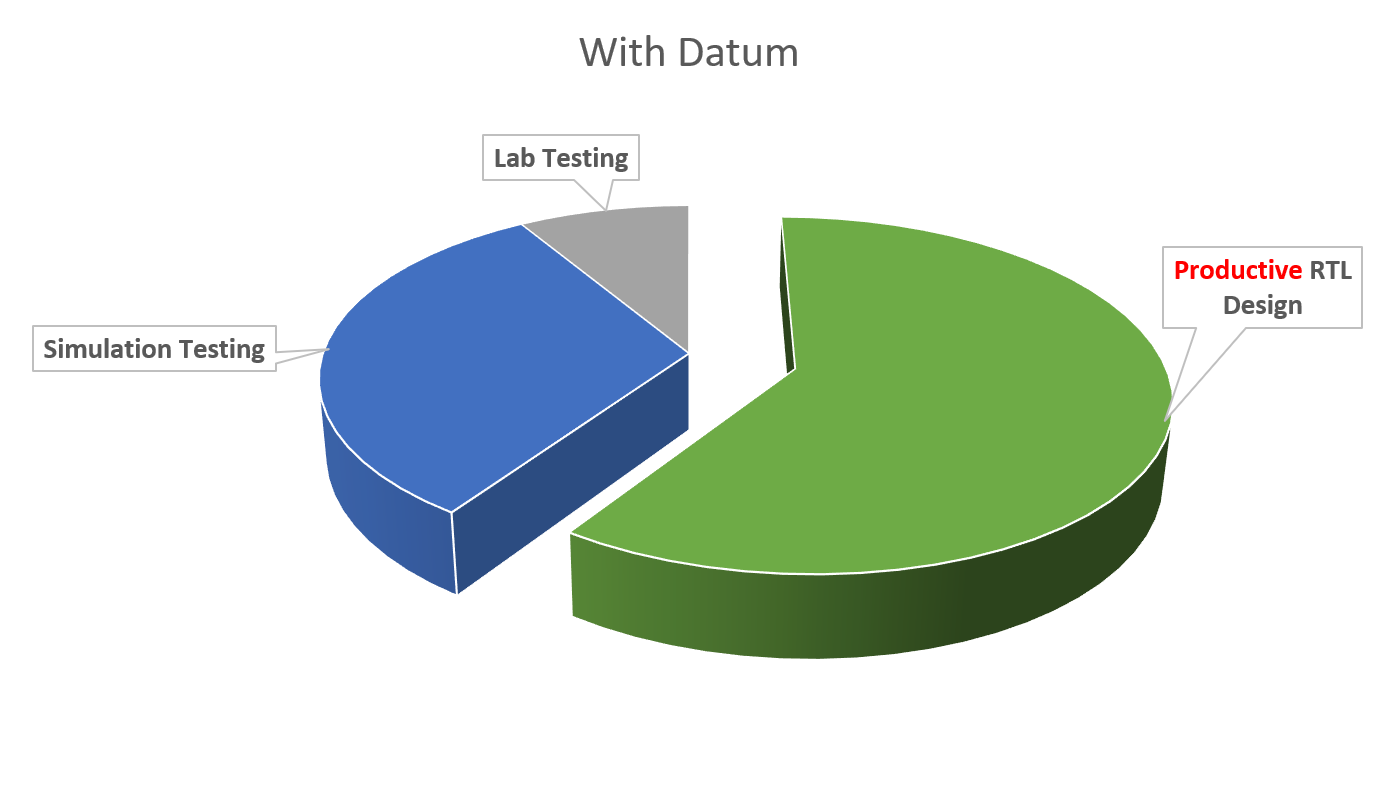

If owners and managers were to track the time spent on feature development vs. operational friction at a fabless design shop without DV Ops and a modern DV approach, they would be horrified. We know they would find low productivity because we have observed homebrew approaches in the field. What seems like a simple task becomes an endless project, becoming a bottleneck to designers and sapping resources.

There is of course overhead in setting up a proper design verification system and a learning curve for designers. Does the effort justify the results?

According to our analysis, the advantages far outweigh the up-front costs when building upon hardened DV Ops tools and proven VIP libraries. After designers spend a week or so learning the ropes, much of the complexity disappears into the fabric of the development stack. This reduces operational friction by: